고정 헤더 영역

상세 컨텐츠

본문

- Capaitor : 전기장 내에서 전기 에너지를 저장하는 소자. Q = CV

- MOSFET에서 Gate 전압이 인가되면, MOS 구조의 Oxide에 전하가 저장되며 capacitor 특성을 가지게 된다.

- 전압에 따른 MOS cap 동작

1. Accumulation

- Vg < 0 인 전압이 인가되었을 때, 금속쪽에 음전하가 모이고 같은양의 양전하가 반도체의 표면에 축적된다. (정공 축적)

- 반도체의 표면에서 원래 p - type 반도체의 도핑에 의한 정공 농도보다 더 큰 정공 농도를 가지게 된다.

2. Depletion

- Vg > 0인 경우, 금속쪽에 양전하가 모이고 반도체의 표면에 같은 양의 음전하가 모인다. 이에 반도체 표면 근처에서 정공이 deplete 되고 depletion region이 형성된다. 반도체 표면에서 원래 p - type 반도체의 도핑에 의한 정공 농도보다 더 작은 정공 농도를 가지게 된다.

3. Weak Inversion

- Vg >> 0인 경우, 금속 쪽에 가해지는 전압의 크기가 더욱 증가하면 반도체 표면의 에너지 밴드가 더 강하게 아래로 휘어지게 된다. 충분히 큰 전압은 반도체 표면의 Ei를 Ef보다 아래로 휘게하고 이에 conduction band에서 큰 전자 농도를 가지게 된다. 이 n - type 표면층은 도핑에 의해 형성된 것이 아니라, 금속에 가해진 전압에 의해 원래의 p - type 반도체가 inversion 되면서 형성된다.

4. Strong Inversion

- Weak Inversion인 경우보다 더 큰 크기의 Vg가 인가된 경우로, 반도체 기판에서 p - type 인 것만큼 표면이 n - type 으로 된 상태이다.

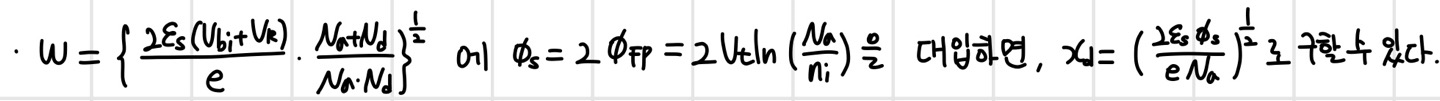

- Depletion layer Thickness

- N substrate 인 경우

- Threshold voltage 구하기

- Work Function difference : metal과 si의 work function이 달라 접합 시 band bending이 발생한다.

- Oxide Charge : Oxide 내부의 다양한 요인들로 인해 Oxide 내부에 전하가 존재.

1. Qm : mobile ionic charge - 양전하 이며 알칼리 금속 이온이 산화 등의 공정 과정 중 풀가피하게 포함되어 생성됨.

2. Qot : oxide trapped charge - 양전하 또는 음전하 이며 SiO2의 불완전함으로 인해 생성됨.

3. Qf : oxide fixed charge - 양전하 이며 Interface 근처는 fixed charge를 가진 transition 층이 존재한다.

4. Qit : Interface trap charge - 양전하 또는 음전하 이며 반도체 결정의 격자가 Si-SiO2 계면에서 갑자기 끝어져 생성됨.

- Flat - Band Voltage : 위 그림에서 밴드가 휘지않게 하기위한 전압.

- Treshold Voltage

* Enhanced Mode : Vg 가 인가되지 않았을 때, channel이 형성되지 않는 mode.

* Depletion Mode : Vg가 인가되지 않아도 channel이 형성되어 있는 mode.

'반도체 > 메모리' 카테고리의 다른 글

| NAND 소자 이해 - 5. 3D NAND Flash의 Issue (0) | 2024.02.18 |

|---|---|

| NAND 소자 이해 - 4. 3D NAND Flash 공정 Process (0) | 2024.02.18 |

| NAND 소자 이해 - 3. 3D NAND 도입 배경 (0) | 2024.02.18 |

| NAND 소자 이해 - 2. NAND Flash Memory 동작 (0) | 2024.02.18 |

| NAND 소자 이해 - 1. NAND Flash Memory란? (0) | 2024.02.15 |