고정 헤더 영역

상세 컨텐츠

본문

- Flash Cell의 구조와 Program Operation 방식

- Vth가 5V라고 가정했을 때, 위의 사진과 같이 일반 MOSFET 처럼 Channel이 형성된 모습을 볼 수 있다. 하지만 이 경우는 정보가 저장되지 않고 전원이 Off되면, 소자도 꺼진다.

- Vth보다 훨씬 큰 전압을 걸어주면, FN Tunneling으로 인해 Channel의 전자가 tunneling oxide를 통과하여 floating gate에 존재하게 된다. 이렇게 되면 5V를 걸어주어도 floating gate의 전자로 인해 Channel이 형성되지 않고 정보가 저장되었다고 할 수 있다.

- 저장된 정보를 지우기 위해선, 정보를 저장할 때 사용한 전압과 반대 전압을 걸어준다. 실제에선 (-)전압을 사용하지 않기 때문에 gate에 0V, body에 12V를 걸어준다. 그러면 전압에 의해 floating gate의 전자가 다시 tunneling을 통해 oxide를 통과해 Channel영역으로 이동하고, 정보가 지워지게 된다.

- 정보를 읽는 방법 : Control gate에 Read전압을 인가하고, Cell에 전류가 흐르면 Erase 상태, 전류가 흐르지 않으면 Program 상태로 읽는다.

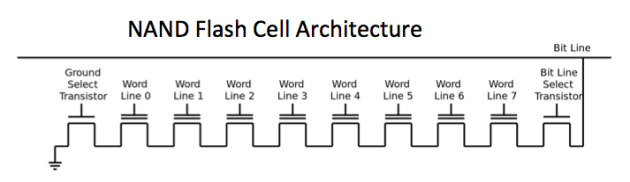

- 2D NAND Flash Cell String

- 위 사진은 2D NAND Cell의 구조를 간략하게 표현한 그림이다. String은 Cell들을 연결한 Cell Array의 최소 단위여며 Program/Read 동작은 String을 통해 Cell에 접근한다. 맨 양쪽의 Cell은 DSL(Drain Select Line), SSL(Source Select Line) 이라고 하며, 다른 Cell보다 크다. 이 Cell들을 통해 String의 접근을 조절한다.

- Cell Array를 control하는 peri회로도 존재하며 이들 전체를 합한 것이 Chip이라고 할 수 있다.

'반도체 > 메모리' 카테고리의 다른 글

| NAND 소자 이해 - 4. 3D NAND Flash 공정 Process (0) | 2024.02.18 |

|---|---|

| NAND 소자 이해 - 3. 3D NAND 도입 배경 (0) | 2024.02.18 |

| NAND 소자 이해 - 1. NAND Flash Memory란? (0) | 2024.02.15 |

| DRAM 소자 이해 - 4. DRAM Process Flow (0) | 2024.02.15 |

| DRAM 소자 이해 - 2. DRAM 동작 원리 (0) | 2024.02.15 |