고정 헤더 영역

상세 컨텐츠

본문

- 3D NAND Flash 4대공정

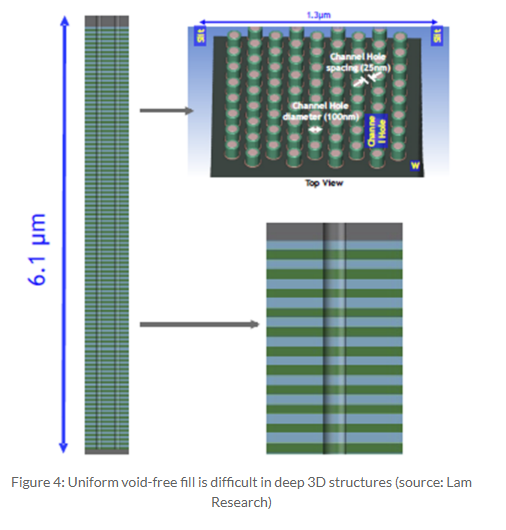

1. Channel Etch (Plug) : Cell의 모음으로 전류가 흐르며, 동작의 기본 단위인 String을 형성하는 공정. SiO2와 Si3N4를 연속해서 증착한 뒤, Channel부분을 형성하기 위해 Etch를 진행한다. 이 영역에 oxide, si를 순서대로 증착하여 Channel을 형성한다.

2. Stair Etch : 층별 WL에 Bias를 전달하기 위한 Contact 연결이 필요햐여 계단형 적층 구조 형성. SiO2와 Si3N4를 한 층으로 총 층수만큼의 계단형 적층구조가 필요하다.

위의 사진처럼 계단형 적층 구조를 형성하여 각 층의 WL에 전압을 Control 한다.

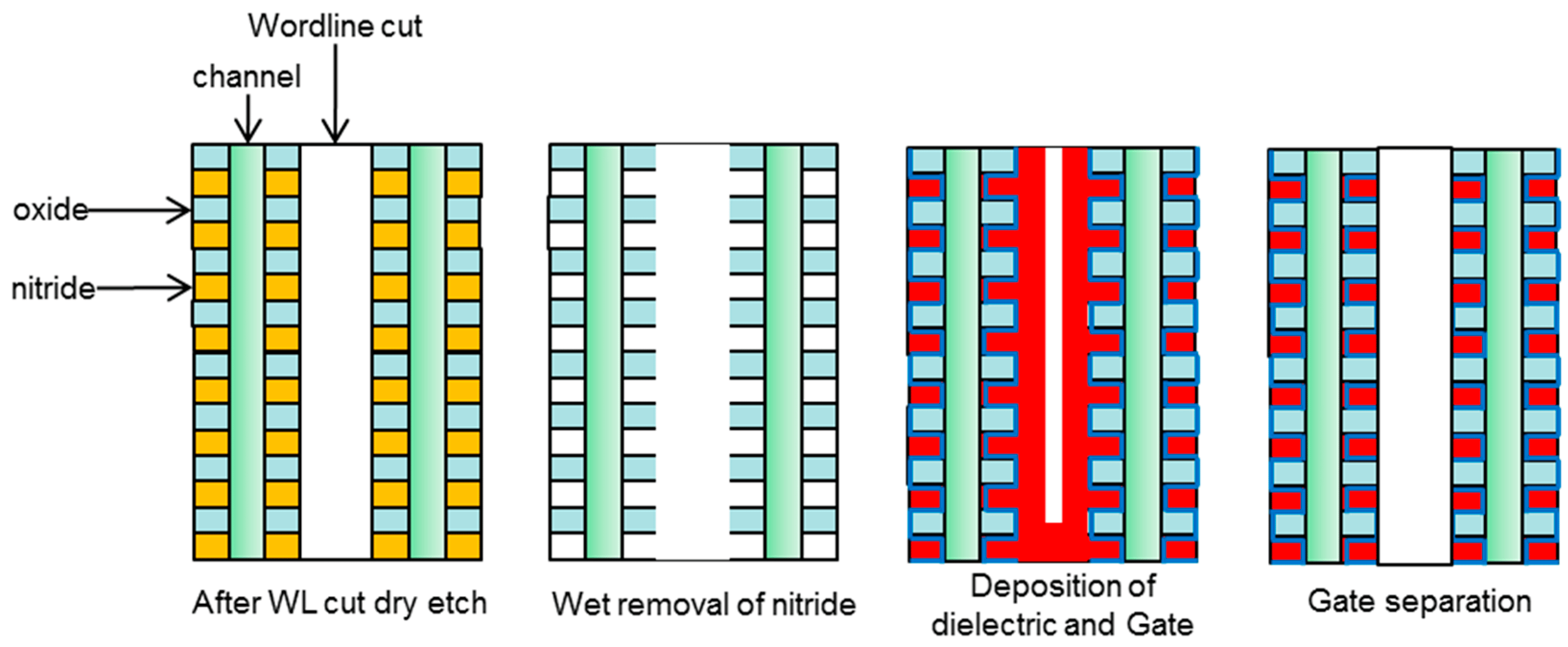

3. WL Cut (Slit) : Plug 간의 구별을 위하여 Plug 사이를 물리적으로 단절시키는 공정이다.

4. Metal Replacement : 원활한 Cell 동작을 위한 WL의 저항 감소 목적으로 Nitride를 제거하고 해당 영역을 Metal로 채우는 공정이다.

- 3D NAND (SMArT) Process : 3권 p.171 참조

1. Laser marking을 통해 wafer에 이름을 새긴다. 그호 peri영역을 형성하고, Plug가 pipe로 연결되는 Pipe-connection Gate 형성을 진행한다.

2. SiO2와 Si3N4를 순서대로 여러층 증착한다. 그후 Plug etch를 진행한다.

3. Plug영역에 Channel을 형성하기 위해 tunneling oxide와 si를 증착한다. (MINIS 구조에서 TiN/W - Al2O3 - Blocking Oxide - Nitride - Tunneling Oxide - Channel Poly 로 형성되는데, Al2O3는 carrier가 없는 nitride에 hole을 주입할 때 큰 전압이 필요하므로 Al2O3의 carrier를 이용해 쉽게 erase한다.

4. Stair etch를 진행한다. X, Y 축으로 계단을 만들어서 Stair영역의 면적을 최대한 작게 형성한다.

5. Slit Pattern 을 통해 Plug을 분리한다.

6. Metal Replacement를 통해 Si3N4를 제거 후 Metal을 증착한다.

7. 맨 위층에 Metal회로를 형성한다.

'반도체 > 메모리' 카테고리의 다른 글

| 반도체 물성 및 소자 2 - 2. MOS 특성 (0) | 2024.02.26 |

|---|---|

| NAND 소자 이해 - 5. 3D NAND Flash의 Issue (0) | 2024.02.18 |

| NAND 소자 이해 - 3. 3D NAND 도입 배경 (0) | 2024.02.18 |

| NAND 소자 이해 - 2. NAND Flash Memory 동작 (0) | 2024.02.18 |

| NAND 소자 이해 - 1. NAND Flash Memory란? (0) | 2024.02.15 |